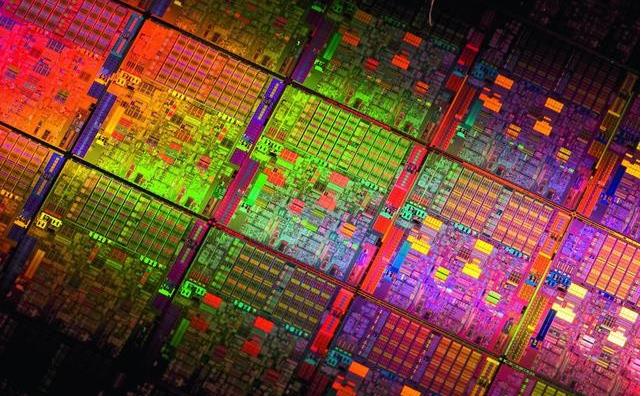

目前很多手机厂商在发布手机的时候,很多时候会提到这款手机使用了某某某芯片,才用了什么22nm、14nm、10nm这些说法,到底这些数值是干什么用的。数值越低对芯片的芯片越好吗。我们来了解一下。

在开始之前,要先了解纳米究竟是什么意思。在数学上,纳米是0.000000001米,但这是个相当差的例子,毕竟我们只看得到小数点后有很多个零,却没有实际的感觉。如果以指甲厚度做比较的话,或许会比较明显。

用标尺实际测量的话可以得知指甲的厚度约为0.0001米(0.1毫米),也就是说试着把一片指甲的侧面切成10万条线,每条线就约等同于1纳米,由此可略为想象得到1纳米是何等的微小了。

骁龙 835 用上了更先进的 10nm 制程, 在集成了超过 30 亿个晶体管的情况下,体积比骁龙 820 还要小了 35%,整体功耗降低了 40%,性能却大涨 27%。深入来说,这几十纳米怎么计算出来的?我们从芯片的组成单位晶体管说起。

纳米制程是什么?

再回来探究纳米制程是什么,以14纳米为例,其制程是指在芯片中,线最小可以做到14纳米的尺寸,下图为传统晶体管的长相,以此作为例子。缩小晶体管的最主要目的就是为了要减少耗电量,然而要缩小哪个部分才能达到这个目的?左下图中的L就是我们期望缩小的部分。借助缩小闸极长度,电流可以用更短的路径从Drain端到Source端。

此外,计算机是以0和1作运算,要如何以晶体管满足这个目的呢?做法就是判断晶体管是否有电流流通。当在Gate端(绿色的方块)做电压供给,电流就会从Drain端到Source端,如果没有供给电压,电流就不会流动,这样就可以表示1和0。

缩小制程有什么好处?

缩减元器件之间的距离之后,晶体管之间的电容也会更低,从而提升它们的开关频率。那么,由于晶体管在切换电子信号时的动态功率消耗与电容成正比,因此,它们才可以在速度更快的同时,做到更加省电。另外,这些更小的晶体管只需要更低的导通电压,而动态功耗又与电压的平方成反比(这时能效也会随之提升)。

最后,推动半导体制造商向更小的工艺尺寸进发的最大动力,就是成本的降低。组件越小,同一片晶圆可切割出来的芯片就可以更多。即使更小的工艺需要更昂贵的设备,其投资成本也可以被更多的晶片所抵消。

知道纳米有多小之后,还要理解缩小制程的用意,缩小晶体管的最主要目的,就是可以在更小的芯片中塞入更多的晶体管,让芯片不会因技术提升而变得更大;其次,可以增加处理器的运算效率;再者,减少体积也可以降低耗电量;最后,芯片体积缩小后,更容易塞入移动设备中(比如手机),满足未来轻薄化的需求。

迈入10nm为什么那么难?

最后,则是为什么会有人说各大厂进入10纳米制程将面临相当严峻的挑战,主因是1颗原子的大小大约为0.1纳米,在10纳米的情况下,一条线只有不到100颗原子,在制作上相当困难,而且只要有一个原子的缺陷,像是在制作过程中有原子掉出或是有杂质,就会产生不知名的现象,影响产品的良率。

如果无法想象这个难度,可以做个小实验。在桌上用100个小珠子排成一个10×10的正方形,并且剪裁一张纸盖在珠子上,接着用小刷子把旁边的的珠子刷掉,最后使他形成一个10×5的长方形。这样就可以知道各大厂所面临到的困境,以及达成这个目标究竟是多么艰巨。